【要旨】

パナソニック株式会社は、連続的に変化するアナログデータを安定的に抵抗値として記憶する強誘電体メモリスタ[1]を、広くデジタル回路として用いられているCMOS回路上に世界で初めて形成することに成功しました。この結果、同じ回路上でデジタル信号をアナログデータとして扱うことを可能にしました。この成果を用いて、電子回路上で「人の思考」の一部を再現するニューラルネットワーク[2]処理に応用した場合、消費電力を最大1/10に削減でき、より大規模なニューラルネットワーク回路への展開が期待されます。

【効果】

強誘電体メモリスタは、従来の0、1で記憶するデジタルメモリに対し、0から1までの任意の中間値をアナログデータとして記憶・再生することできるため、多くの情報を記憶することが可能です。こうしたより多くの記憶情報に基づく、効率的な演算処理により、処理データ量が大きくなるほど、電力消費量の削減率をより高めることができます。この結果、脳の神経細胞の動きを模倣した、いわゆるニューラルネットワーク信号処理回路が実現でき、今後、より複雑・高度化したニューラルネットワーク回路の実現を加速します。

【特長】

本開発は以下の特長を有しています。

- デジタル回路上に結晶性の良い強誘電体メモリスタを形成することで、アナログデータとして効率的に演算処理できるアナログ制御[3]を実現

(パターン認識処理に応用した場合、従来の1/10の消費電力で処理が可能) - 強誘電体メモリスタは、入力電源が無くても、記憶したアナログデータが安定に保持されます。また使用時以外は電源入力の必要がないため、より一層の省電力化に対応

【内容】

本開発は、以下の技術により実現しています。

- (1)CMOS回路上に、シード層[4]を介して強誘電体メモリスタを形成する結晶成長制御技術

- (2)入力されたデジタル信号をアナログ制御により演算した上で、結果を出力するハイブリッド回路設計技術

【従来例】

今後、データ処理は複雑さを増し、そのための消費電力がさらに増大することから、新しい概念の演算を用いた省電力化が求められていました。この問題を解決する有力な候補の一つにニューラルネットワーク回路がありますが、回路上での実現にはアナログデータの高速かつ安定な記憶が不可欠で、これまで実素子での実証がなされていませんでした。

【特許】

国内35件、外国25件(出願中含む)

【備考】

本開発の一部は、2013 Symposia on VLSI Technology and Circuits(2013年6月11日〜14日、京都市)にて発表します。

【お問い合わせ先】

- R&D本部 広報担当

- E-mail:crdpress@ml.jp.panasonic.com

【内容の詳細説明】

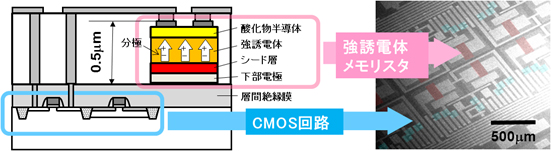

1)CMOS回路上に、シード層を介して強誘電体メモリスタを形成する結晶成長制御技術

CMOS回路は最表面が絶縁性を有する膜で覆われています。この膜は隣り合う原子の配列が整合された状態では形成されていません。このため、直接CMOS回路上に強誘電体メモリスタを形成しても、強誘電体の原子の配列に歪みが生じ、アナログデータの良好な記憶・保持特性が得られませんでした。今回、原子が規則正しく配列し、かつ原子間の距離が強誘電体に近い数値をもつ材料をシード層として選択することで結晶成長の方向が整い、結晶性の良い強誘電体メモリスタを形成することに成功しました。

2)デジタル信号に対するアナログ制御を実現するハイブリッド回路設計技術

ニューラルネットワーク回路は脳の神経細胞の信号処理の仕組みをモデル化した回路です。この回路の信号処理では、複数の演算素子間はパルス信号と呼ばれるデジタル信号で情報をやり取りし、演算素子内部では、パルス信号を電流として用いたアナログ演算を行っています。デジタルとアナログという異なる性質の演算処理をシームレスに行うハイブリッド回路の設計に成功しました。

【用語の説明】

- [1]強誘電体メモリスタ

- メモリスタは、流れた電流量によって抵抗値が変わり、その状態を保持する機能を持ちます。この素子は、抵抗、コンデンサ、インダクタに続く「第4の受動素子」として、1970年代にその存在が理論的に予言されました。当社は強誘電体という材料を用いて、メモリスタに近い機能・動作を実現できることを見出し、2010年6月に発表いたしました。この素子を「強誘電体メモリスタ」と呼んでおります。

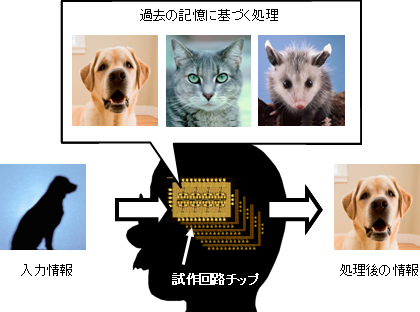

http://panasonic.co.jp/corp/news/official.data/data.dir/jn100624-3/jn100624-3.html - [2]ニューラルネットワーク

- 最初に、望んだ出力信号が得られるように、入力信号に対する重み付けを変化させます。重み付けは抵抗値で表現できますが、強誘電体メモリスタは抵抗値の変化が大きいので、ニューラルネットワークの重み付けに適しています。次に、複数のデータを学習後、メモリスタの抵抗値が変化しないようにして判断したいデータを入力すると、学習させたデータ群の中から入力データに近いものが出力されます。これにより瞬時に柔軟判断することが可能となります。

- [3]アナログ制御

- 強誘電体メモリスタにデジタル信号を通すと、その抵抗値が小さいほど多くの電流が流れます。これはアナログ制御の掛け算に相当します。電流をコンデンサに蓄えるとアナログ制御の足し算となります。これらを組み合わせ、多数の強誘電体メモリスタからの電流をコンデンサに蓄えることで、簡単な構成で低消費電力のアナログ積和演算が実現できます。このような効率的処理により、処理データ量が大きくなるほど、電力消費量の削減率をより高めることができます。

- [4]シード層

- 強誘電体は下地層の影響を強く受けて成長します。そこで、強誘電体と結晶構造が同じで隣り合う原子の距離が近い材料を下地層として形成しておくことで、結晶性の良い強誘電体層を形成することに成功しました。結晶成長の種(シード)として作用することから、この下地層をシード層と呼びます。

強誘電体メモリスタをCMOS回路上に形成した試作回路

(左図:断面構造図 右図:電子顕微鏡写真)

本開発技術を適用した将来的な情報処理イメージ