2026年4月28日

- 製品・サービス

- トピックス

- ナノイー

Adobe Acrobat Readerの特定のバージョンに、一部のPDFが開けないバグが発生しております。PDFが開けない場合、お使いのAcrobat Readerを最新版へアップデートの上お試しください。

2021年6月22日

製品・サービス / プレスリリース

先端半導体パッケージの実装信頼性を向上

板厚精度に優れ、サブストレートとICチップとの接合を安定化

パナソニック株式会社 インダストリアルソリューションズ社は、実装時に低熱膨張性で反りを抑制するとともに、最適な伸縮性と緩衝性で、はんだボールへの応力低減を実現した高実装信頼性の「半導体パッケージ基板材料(品番:R-1515V)」を製品化しました。2021年7月より量産を開始します。

IoT、AIテクノロジー、カーエレクトロニクス化を支える半導体は、高性能化・高集積化が進展しています。これに伴い半導体パッケージは、大型化や2.5Dパッケージ[1]に見られる高密度化が進み、高い実装信頼性が求められています。

当社は、マザーボード用基板材料および半導体材料として半導体パッケージ基板(サブストレート)材料、半導体封止材などの複数の材料を開発しております。この度、これらの独自の開発技術を擦り合わせることで、高い実装信頼性が得られるサブストレート材料を開発しました。実装信頼性を高めるには、ICチップとサブストレートの実装(一次実装)時に反りの発生を抑制することに加え、半導体パッケージとマザーボードの実装(二次実装)時にはんだボールに発生する応力を低減する必要があります。

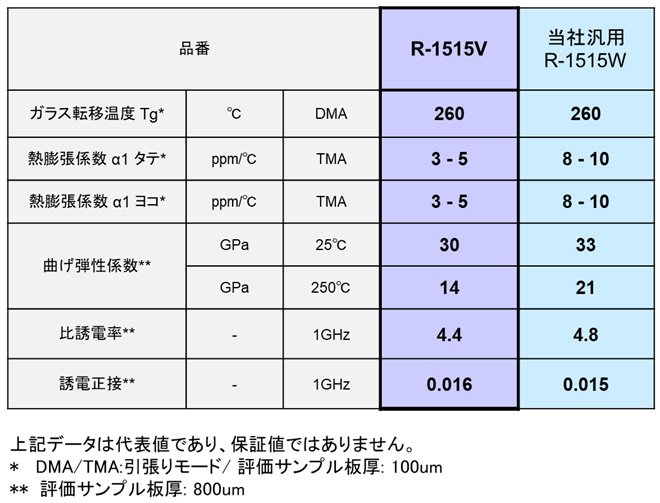

開発した材料は、熱膨張率(CTE[2])を抑え、ICチップの低いCTEに近づけることで反りの発生を抑制し一次実装の信頼性を高めます。さらに優れた板厚精度によりサブストレートとICチップとの接合を安定させ、一次実装の信頼性の更なる向上に貢献します。二次実装においては、熱膨張差ではんだボールにかかる応力を伸縮性と緩衝性を合わせ持つことにより緩和させ、実装信頼性を向上させます。

CPU[3]、GPU[4]、FPGA[5]、ASIC[6]等のFC-BGA[7]パッケージ

「The 2021 IEEE 71st Electronic Components and Technology Conference」(2021年6月1日~7月4日)において紹介。

電子回路基板材料の開発で培った樹脂設計技術で、4ppm(当社測定値)の低熱膨張率材料を開発。ICチップ(半導体)の低い熱膨張率により近づけ、相互の熱膨張率の差により発生する反りを抑制でき、サブストレートとICチップの実装信頼性を高めます。

シミュレーションの結果を基に、独自の樹脂設計技術で、低熱膨張性を確保しつつ伸縮性と緩衝性を合わせ持つ材料を開発しました。これにより、半導体パッケージとマザーボードの間のはんだボールにかかる応力を吸収し分散させることで、一次実装品質に影響を及ぼさず、二次実装の信頼性を向上させます。

回路基板材料開発で培った樹脂流動制御技術で、樹脂流れを抑制しながら成形性の確保を可能にし、厚みのばらつき極少化を実現。これによりサブストレート(コア材)とICチップとの接合を安定させ、一次実装の信頼性を更に向上させます。

インダストリアルソリューションズ社 電子材料事業部

https://industrial.panasonic.com/cuif/jp/contact-us?field_contact_group=2201&field_contact_lineup=3248&ad=press20210622jp

以上

記事の内容は発表時のものです。

商品の販売終了や、組織の変更などにより、最新の情報と異なる場合がありますので、ご了承ください。